科学家已经开发出了可定制计算设备 可以最大程度地提高人工智能应用的效率

来源:

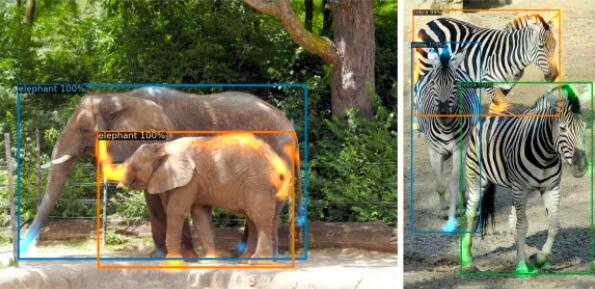

大阪大学的科学家使用现场可编程门阵列(FPGA)构建了一种新的计算设备,用户可以对其进行定制,以最大程度地提高人工智能应用的效率。与当前使用的可重新布线硬件相比,该系统将电路密度提高了12倍。而且,预计可将能耗降低80%。这一进步可能会导致灵活的人工智能(AI)解决方案,该解决方案可提供增强的性能同时消耗更少的电能。

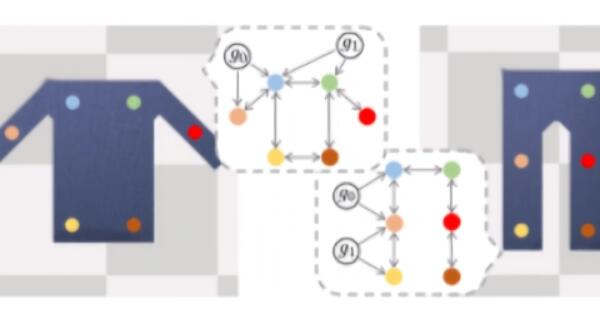

人工智能已成为几乎所有消费者日常生活的一部分。像Uber这样的智能手机应用程序,Gmail的垃圾邮件过滤器以及Siri和Nest等智能家居设备都依赖于AI。但是,实施这些算法通常需要大量的计算能力,这意味着大量的电费以及大量的碳足迹。可以重新连接的系统(例如人脑)可以为每个任务优化计算机电路,从而大大提高了能效。

通常,我们认为硬件是由制造商确定的,其中包括计算机处理器的物理逻辑门和晶体管。然而,现场可编程门阵列是专用逻辑元件,用户可以将其“现场”重新布线以用于定制逻辑应用。研究团队使用了非易失性“通孔开关”,这些通孔保持连接状态,直到用户决定重新配置它们为止。使用新颖的纳米加工方法,他们能够将十二倍的元素填充到类似网格的“横杆”布局中。通过缩短电子信号需要路由的距离,设备最终所需的功率减少了80%。

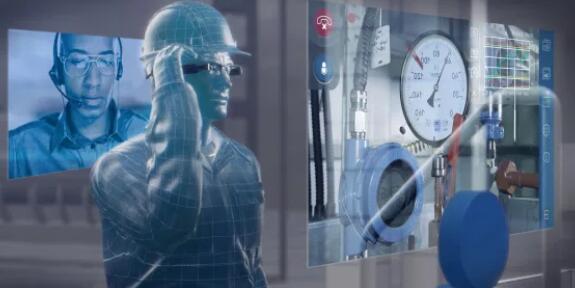

第一作者Masanori Hashimoto说:“我们基于现场可编程门阵列的系统的设计周期非常快。如果需要,可以每天对其进行重新编程,以使每个新的AI应用程序获得最大的计算能力。”通孔开关的使用也消除了对以前的FPGA器件所需的编程硅区域的需要。

高级作者Jaehoon Yu说:“ Via-switch FPGA适合用作最新AI算法的高性能实现平台。”

郑重声明:本文版权归原作者所有,转载文章仅为传播更多信息之目的,如有侵权行为,请第一时间联系我们修改或删除,多谢。